- 同袍存储专注于企业级机械硬盘、监控专用硬盘、服务器固态硬盘、专业显卡等代理分销

- 服务热线:18337524633

什么是存储控制器?

存储控制器是是计算机与磁盘驱动器的接口设备,是磁盘阵列的大脑,硬件组成包括CPU,高速缓存(Cache)以及光纤通道(FC),主要用来实现数据的存储转发以及整个阵列的管理,是系统主机与存储器件(磁盘柜)之间的“桥梁”。

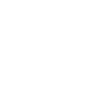

存储控制器在存储设备中发挥着非常重要的作用。存储控制器是一台控制着存储阵列的设备,主要包括三种类型的组件:"CPU"、"缓存存储器"和"与网络和存储设备的连接接口"。

▲存储控制器一览

存储控制器将多个存储设备中的存储区域整合起来,作为一个存储区域提供给服务器。当收到来自服务器的写入数据的请求时,存储控制器将确定数据落到哪个存储设备,并将数据存储在所选设备中。

当收到来自服务器的读取某些数据的请求时,存储控制器找到相关数据的存储位置,从存储设备中读取数据,并将其传输到服务器。高效、稳定地完成这些处理任务是存储控制器的作用。

除了读写数据外,存储控制器还执行处理任务,实现各种增值功能包括RAID、卷管理(volume management)、Provisioning、快照(snapshot)、克隆(clone)、复制(replication)等。

存储控制器的几种主要模式

如前面的视频所述,最早的存储只有单个控制器,如果它坏了,那么整个业务都会因此停顿。因此,至少两个控制器非常有必要。现如今的存储已大多是双控制器了,但即使是这样,依然有很多不同,挑选存储产品时可要擦亮眼睛了。下面就来介绍几种主要的双控模式。

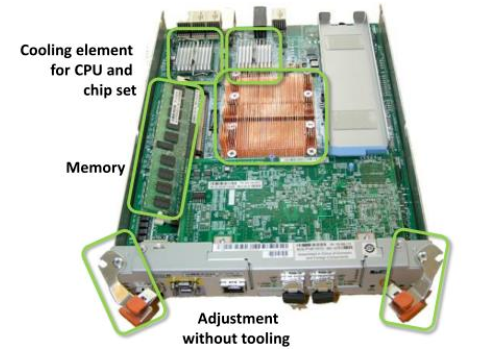

双控制器,主动/被动模式(Active/Passive)

正常运行时,两个控制器中的一个处理所有的I/O处理和数据服务管理(主动),而第二个控制器则随时待命(被动),准备在发生故障时接管。后来有一些改进允许在被动控制器的主机端口上接收和传输I/O,但控制器本身不进行I/O或数据服务处理。

相反,它只是通过内部连接将I/O传递给主动控制器,主动控制器负责所有数据服务(如重复数据删除、快照、RAID等)以及对底层闪存介质的所有读/写处理。这就需要使用ALUA(非对称逻辑单元访问)来定义到主动控制器的首选路径和到被动控制器的非首选路径。

存储处理器在其中主动提供对给定 LUN 的访问权限的系统。其他处理器用作备用 LUN,并且可以主动提供对其他 LUN I/O 的访问权限。只能向给定 LUN 的主动端口成功发送 I/O。如果通过主动存储器端口访问失败,则其中一个被动存储处理器可通过服务器对其进行访问而激活。

主/被架构是上世纪80年代发展起来的原始HA机制。这种模式在当今已经被淘汰了,用户在选择存储时应避免选择这种架构,特别是对有些厂商来说,这种HA架构实现起来更简单,有助于实现产品快速上市。主/备架构最大的劣势是,主动控制器很快就会成为性能瓶颈,而被动控制器则处于闲置状态,性能完全浪费。

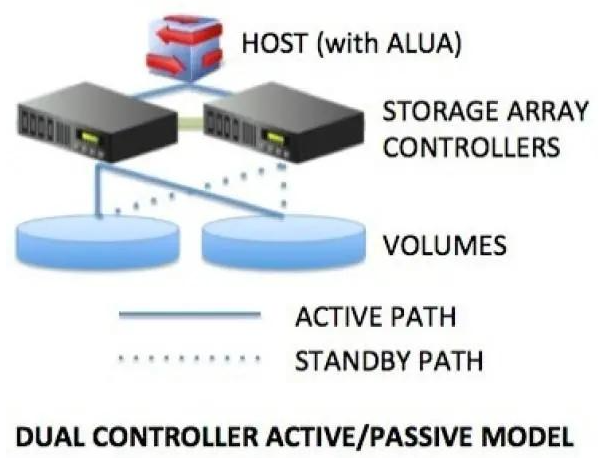

双控制器、双主动模式(Daul Active)

这种设计是对主动/被动模式的改进,使用两个控制器来执行全部的数据活动。其特点是,每个控制器都是卷的子集的主节点,并在发生故障时,随时准备接管伙伴的卷。这比完全的主动/主动架构(任何卷在任何控制器的任何端口上都可以访问,并且没有路径或性能偏好)更容易实现。

但其缺点是,任何给定的卷仍然受限于单个控制器的资源,一旦发生故障,阵列的性能可能会减半。另一个问题是,管理员必须关注每个控制器上的工作负载,并手动分配卷以保持平衡。

双控制器,主动/主动模式(Active-Active)

这是当前最流行的双控制器架构形式,两个控制器在数据服务和I/O处理中都是主动的,没有给控制器分配卷,任何主机都可以通过任何控制器上的任何端口访问任何卷,而不会有路径或性能上的损失。允许通过所有可用的存储器端口同时访问多个 LUN,而不会明显降低性能。所有路径始终保持活动状态,除非路径发生故障。

多控制器、非对称双主动模式(Asymmetric Dual-Active)

这种模式类似于双主动模式,不同之处在于,现在可以有两个以上的控制器。卷仍然由某个控制器拥有,仍然有路径和性能偏好。这种架构的优势是聚合规模–在单点管理下获得更高水平的总容量和性能。然而,任何特定的卷仍然受限于拥有它的控制器的性能。

支持非对称逻辑单元访问 (ALUA)。ALUA 合规存储系统对每个端口提供不同级别的访问。ALUA 允许主机确定目标端口的状态,并区分路径的优先级。主机会将某些活动路径用作主路径,其他用作辅助路径。

多控制器,N路对称主动模式(N-way Symmetric Active)

在这种模式下,存储阵列可扩展到N个控制器。正常运行期间,所有控制器都积极地服务于I/O和处理数据服务,并均匀地分担工作负载。如果其中一个控制器发生故障,其余的控制器将继续为所有的I/O服务。

在故障期间,N-1个控制器依然为客户请求提供服务。系统性能随着控制器的增加而线性扩展,反之亦然。例如失去4个控制器中的1个会造成最大25%的资源损失。

发表评论

站内搜索

采购报价请联系

相关推荐

Copyright 2020-2026 同袍存储 粤ICP备2021121885号网站地图